# Nanostencil Lithography and Nanoelectronic Applications

Oscar Vazquez, Marc van den Boogaart, Dr. Lianne Doeswijk, Prof. Juergen Brugger, *LMIS1* Dr. Chan Woo Park, *Visiting Professor* Dr. G.M. Kim, D. Grogg, *Former members*

Laboratoire de Microsystèmes Ecole Polytechnique Fédérale de Lausanne (EPFL) Switzerland

### **Outline**

### 1. LMIS1 Activities

### 3. Challenges & Development

### 2. Nanostencil Technique

### 4. Nanoelectronics

### LMIS 1 Microsystems and Nanoengineering

- Integration of micro and nanotechnologies into functional and advanced devices

- Alternative technologies to achieve sub-micron resolution at low-cost and with high throughput

- Integration of life-science technologies with current fabrication technologies for Lab-on-Chip devices.

Slide 3

### LMIS 1 Microsystems and Nanoengineering

Imis1.epfl.ch

ÉCOLE POLYTECHNIQUE Fédérale de Lausanne

### LMIS 1 Microsystems and Nanoengineering

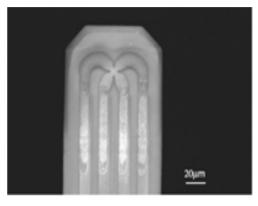

#### **Bismuth Hall sensor**

#### NEMS

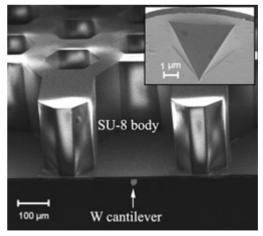

### Conducting AFM probes

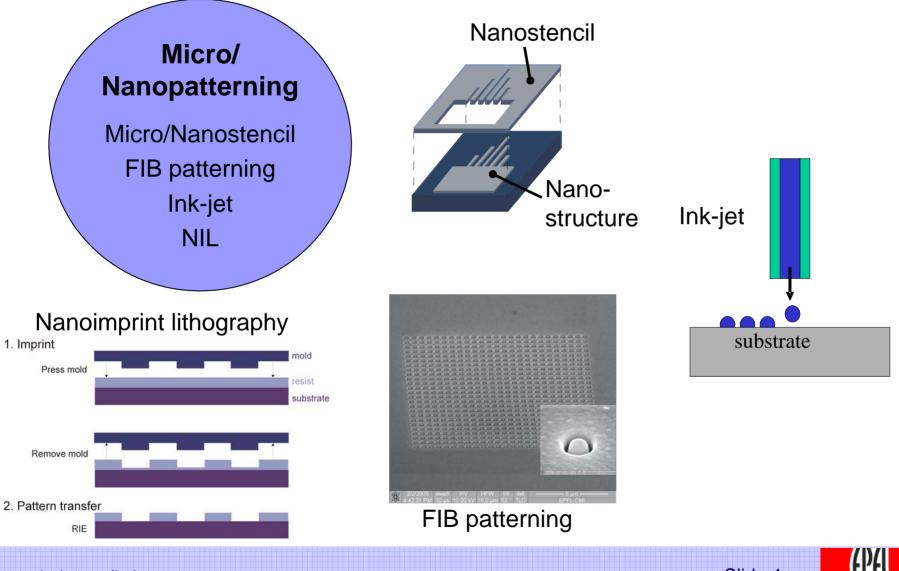

### **Emerging Patterning Methods**

| Soft-lithography                               | Nanoimprint<br>lithography                                    | Nanostencil<br>lithography                               |

|------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|

| Ink delivery<br>molecules, wet<br>soft-contact | Thermo-mechanical,<br>nano-imprinting,<br><i>hard contact</i> | Local deposition<br>stencil, vacuum<br><i>no contact</i> |

| Soft FDMS stamp                                | Hard master<br>Hard master<br>Substrate<br>Polymer            | Vacuum deposition<br>Stend<br>Substrate                  |

|                                                | →II ← 10 nm<br>10 nm<br>Candidate fo<br>Integrated 0          |                                                          |

| 4 and ab                                       |                                                               | Slide 6                                                  |

Imis1.epfl.ch

Slide 6

ÉCOLE POLYTECHNIQUE Fédérale de Lausanne

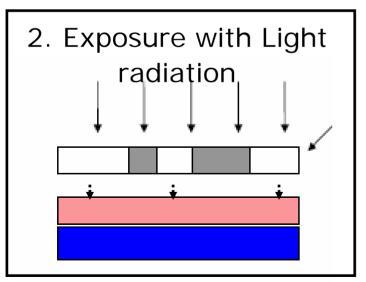

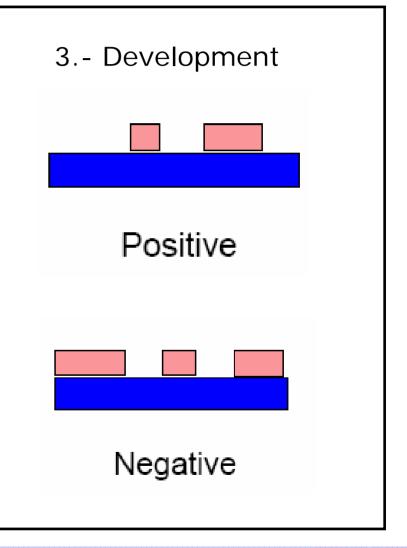

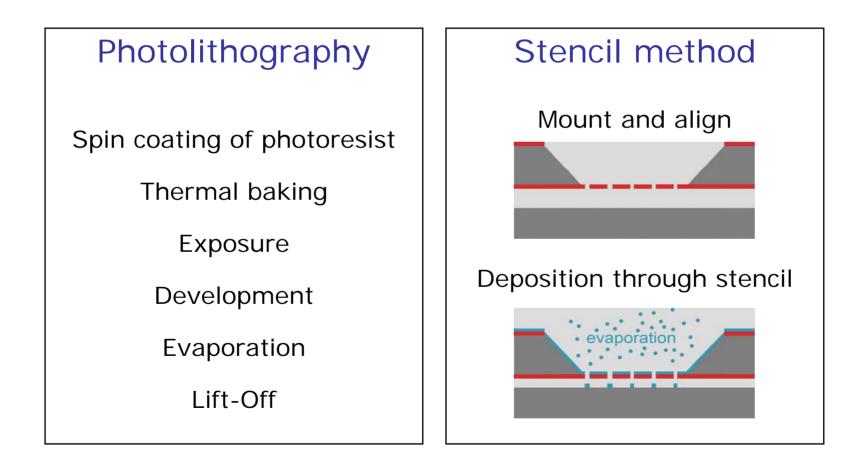

# Photolithography

# **Stencil lithography Etching** By etching, materials like Silicon, $SiO_2$ can be patterned. Lift-Off is also used to make metallic patterns 2 1 deposit thin film of desired material coat and pattern photoresist 3 4 etch film using photoresist as mask remove photoresist

lmis1.epfl.ch

Slide 8

### **Stencil technique**

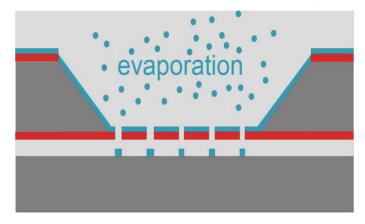

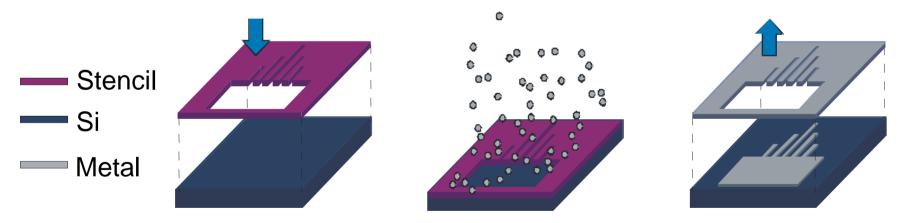

The Nanostencil technique is a patterning method based on shadow mask evaporation.

A thin membrane is used as a solid mask to transfer the patterns from the membrane to the substrate during the evaporation

Slide 9

### **Basic Principle**

### Examples

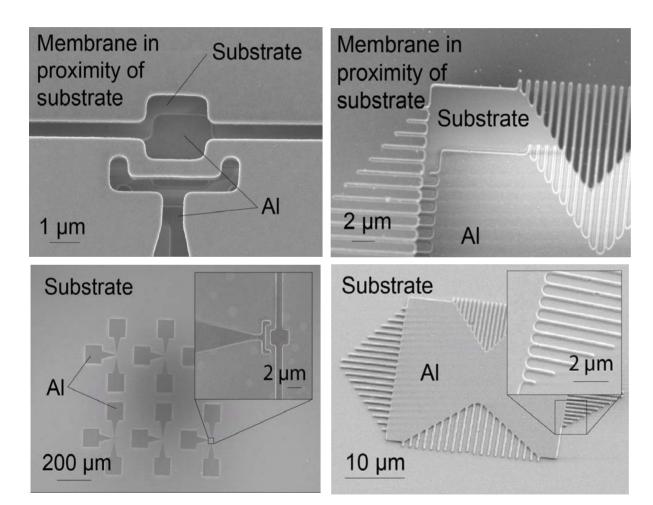

### Top images: Stencil and substrate after evaporation

Bottom images: Resulting micro/nano structures after removal of stencil

Slide 11

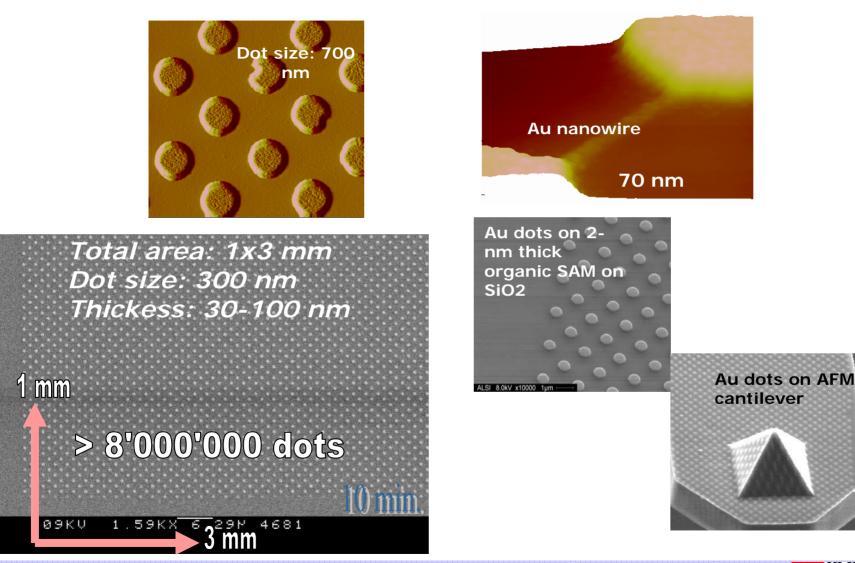

### **Examples**

*J. Brugger et al., Microelectronic Engineering 53 (2000) 403-405* Imis1.epfl.ch

### Simple process

Stencil method is much simpler since it does not need any photoresist treatment

Slide 13

# Main advantages

- No resist, development or baking → Clean and Soft technology

- Non-contact → Prepatterned, Fragile, non-planar, functionalized, CMOS, MEMS substrates

- <u>Re-usable</u> → Rapid and low-cost patterning

- Micro and nanostructuring in a single step →

Wide range of size features

- <u>High Flexibility of materials</u> → Metals, Oxides (PLD), Piezoelectrics (PLD), SAMs

Slide 14

### **Potential Applications**

- Nanoelectronics (High throughput with <1um nanometer resolution)</li>

- Nanobiotechnology (Patterning of Inorganic-Organic interfaces)

- Nanoscale material science (High flexibility of materials)

- Sensors

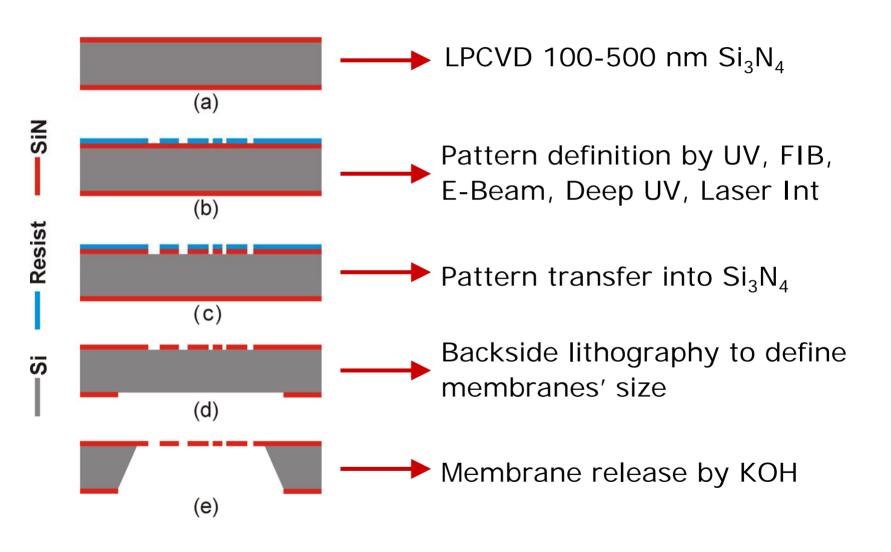

### **Fabrication of the Stencil**

# **Challenges: Clogging**

Clogging occurs due to the accumulation of deposited material on top and inside the membrane apertures.

Features' size is reduced as the material is evaporated.

Slide 17

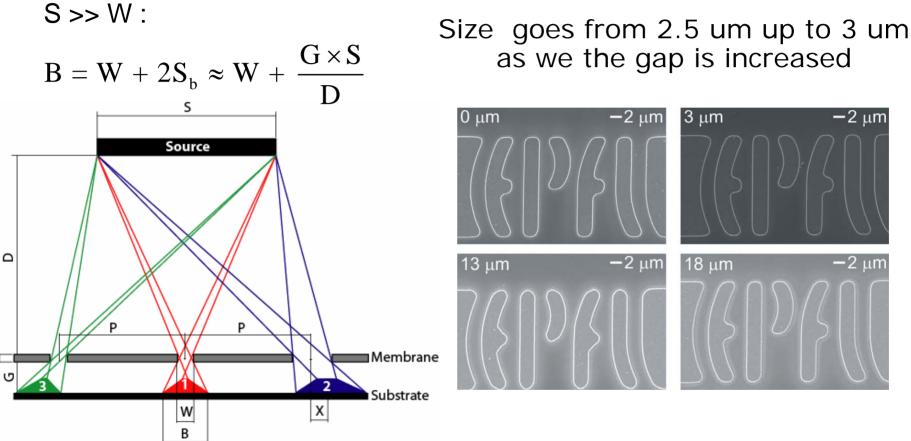

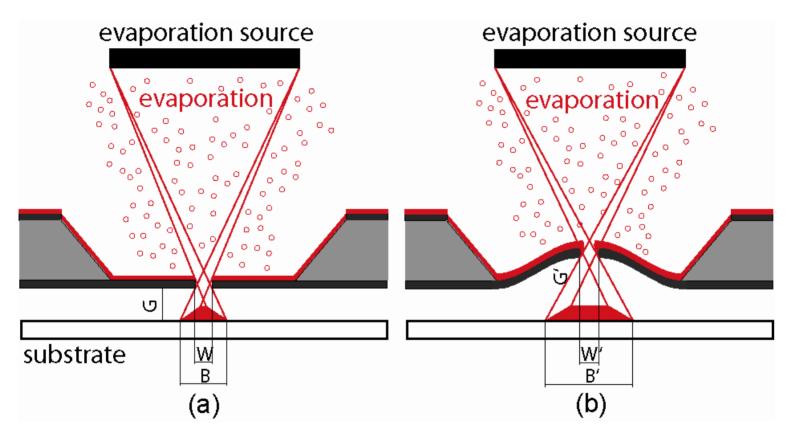

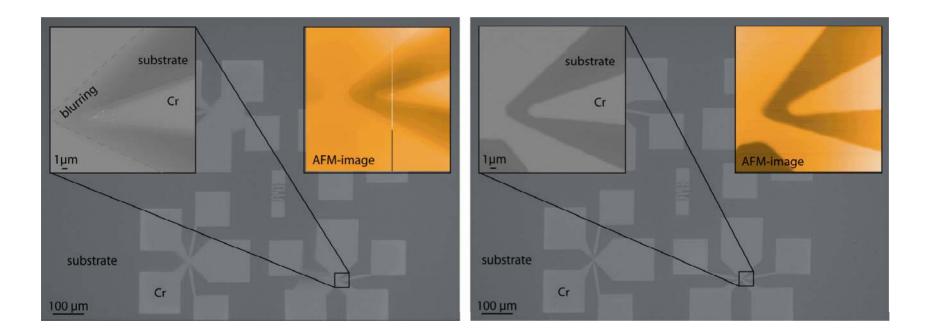

# **Challenges: Blurring**

Blurring: Geometry, Diffusion and Evaporation method.

### **Challenges: Deformation**

The deformed membrane induces both an increased gap and an altered aperture shape.

### Main achievements

# Nanostencils

(FIB)

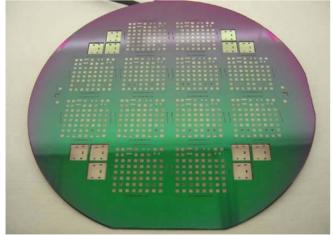

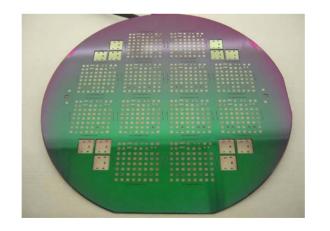

**Full-wafer stencils**

(DUV/MEMS)

# Stabilized stencils

Nanoslits and Rapid Prototyping

High Throughput with Micro - and Nanometer apertures Deformation reduced up to 96%

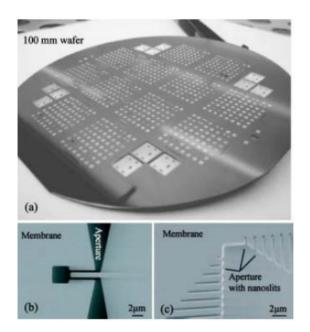

### **Full wafer stencil with DUV**

Full 4" wafer stencil with micro and nanometer apertures Features from 200 nm up to 300 um were transfered into a substrate in a single evaporation step

HIGH THROUGHPUT!!

## **Reinforced Stencils**

Use rims to increase the stiffness of the membrane

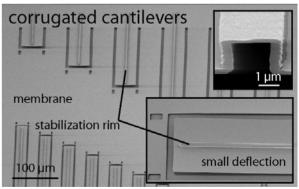

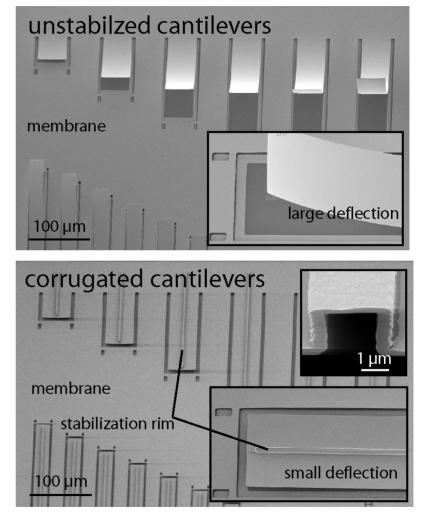

### Top image:

- Cantilever-like membranes.

- Large deflection due to deposition induced stress

### Bottom image:

- Stabilized cantilever-like membranes.

- Small deflection due to stabilization rims

### Improved Pattern transfer

# Surface pattern made by non-stabilized stencil

# Surface pattern made by stabilized stencil

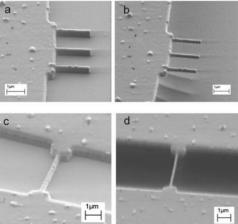

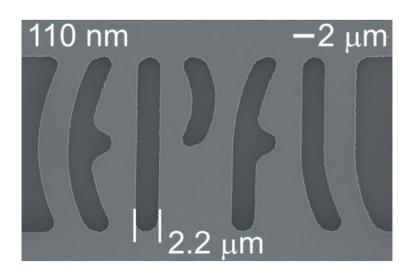

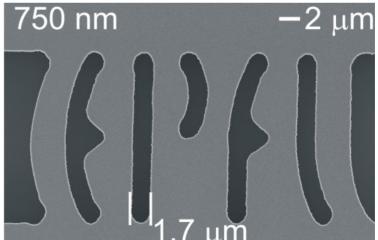

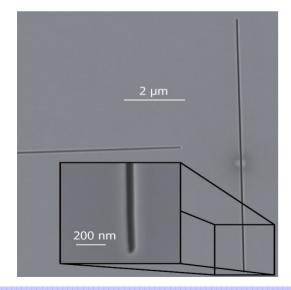

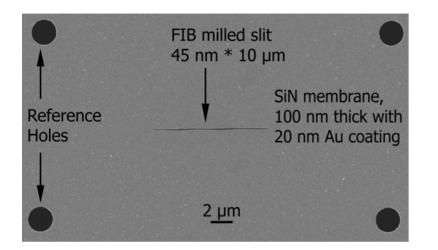

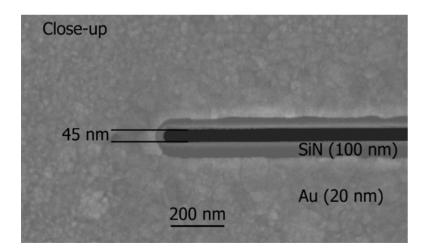

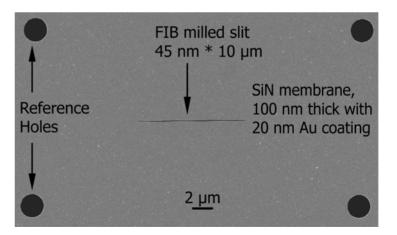

### **Nanostencils by FIB**

- ➢ SiN thickness: 100 nm

- Sub-100 nm width slits made by FIB

- > Length: 10um

- 20 nm Au deposited on SiN to avoid charging during FIB

### **Applications for Micro and Nanoelectronics**

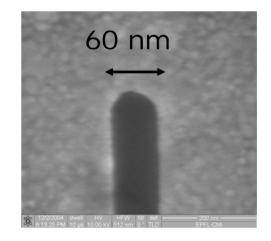

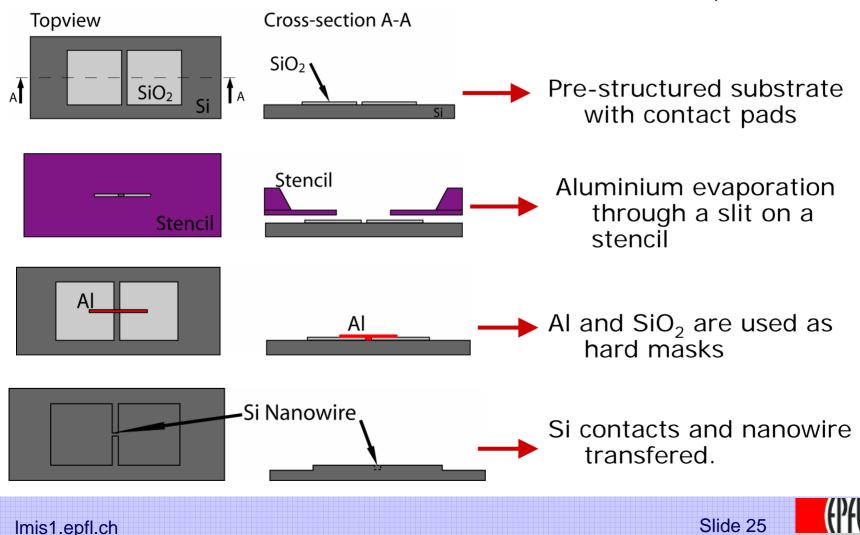

Nanowires based on Stencil Technique (Developed by Daniel Grogg, now in LEG)

FÉDÉRALE DE LAUSANNI

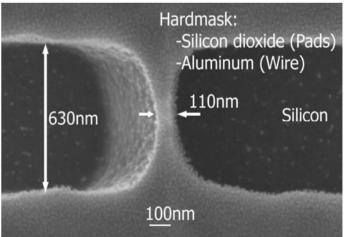

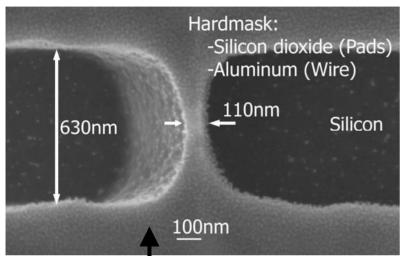

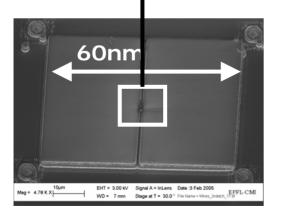

### **Applications for Micro and Nanoelectronics**

Si Wire 110nm between contact pads after RIE etching.

### Stencil fabricated with Photo-Litho and FIB

## **Applications for Micro and Nanoelectronics**

*Outlook: Integration with CMOS technology and architectures*

- Fabrication of Si wires <100 nm.

- I/V characterization (Temperature and Gate V)

- Develop CMOS/SiNW devices (with LEG, Prof. Ionescu)

- Fabrication NW/CMOS arrays (with LEG, Prof. Ionescu)

- Develop fault tolerant circuits (with LSM, Prof. Leblebici)

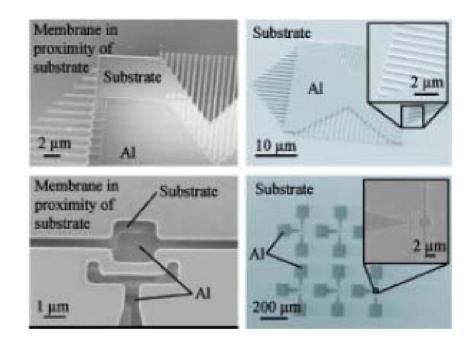

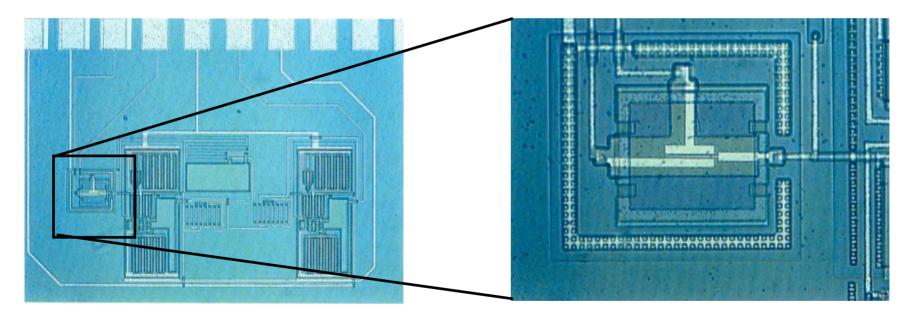

### Nanoresonators on CMOS chip

in collaboration with Julien Arcamone CNM-CSIC, Institut de Microelectronica de Barcelona.

Nanostencil can be used for fabrication on pre-defined structures.

### CMOS chip

Post-process: AI pattern using nanostencil

Slide 28

### Acknowledgments:

- Project supported by SNF

- Europe Union project NAPA

- CMI for technology support and contribution

Thanks to the Integrated Systems Centre

http://lmis1.epfl.ch